## RECONFIGURABLE NETWORK-ON-CHIP (NoC) ARCHITECTURES FOR EMBEDDED SYSTEMS

by

Salih Bayar

B.S., Electronics and Communication Engineering, Yıldız Technical University, 2003, İstanbul, Turkey

M.S., Systems Engineering, Electronics and Information Technology, University of Karlsruhe(TH), 2007, Karlsruhe, Germany

> Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate Program in Computer Engineering Boğaziçi University

2015

## RECONFIGURABLE NETWORK-ON-CHIP (NoC) ARCHITECTURES FOR EMBEDDED SYSTEMS

#### APPROVED BY:

| Assoc. Prof. Arda Yurdakul            |  |

|---------------------------------------|--|

| (Thesis Supervisor)                   |  |

|                                       |  |

| Prof. Oğuz Tosun                      |  |

|                                       |  |

| Assoc. Prof. Sıddıka Berna Örs Yalçın |  |

|                                       |  |

| Assoc. Prof. Alper Şen                |  |

|                                       |  |

| Assist. Prof. Faik Başkaya            |  |

DATE OF APPROVAL: 16.12.2014

To the memory of my beloved Father...

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor Assoc. Prof. Arda Yurdakul. Without her guidance and support, it would be impossible to come to the end of this thesis.

I am also very grateful to Prof. Oğuz Tosun and Assoc. Prof. Sıddıka Berna Örs Yalçın because of their valuable support and recommendations during my thesis. I would also like to thank Assoc. Prof. Alper Şen and Assist. Prof. Faik Başkaya for their participation in my thesis committee and for their helpful comments to improve this thesis.

I would like to express my very great appreciations to Dağhan Dinç for his valuable help in the development of Systematic Resampling Algorithm. Advices given by Coşkun Çelik and Assoc. Prof. Süleyman Tosun have been great help in modifying NIRGAM NoC Simulator. I would like to thank Ömer Çoğal for supplying numeric test values for NoC, Prof. Smail Niar and Assist. Prof. Betül Demiröz for their supports, suggestions and corrections in case studies.

This thesis work is supported by The Scientific and Technological Research Council of Turkey, TÜBİTAK (Project Nr.: 104E038), Boğaziçi University Scientific Research Projects (Project Nr.: 06M105, 09A103P, 5578) and State Planning Organization of Turkey, DPT under grant no 2007K120610.

#### ABSTRACT

## RECONFIGURABLE NETWORK-ON-CHIP (NoC) ARCHITECTURES FOR EMBEDDED SYSTEMS

Communication architectures such as Point-to-Point (P2P) and shared bus are poorly scalable as the number of cores or the communication volume increase. Networkon-Chip (NoC) has been proposed to reduce power consumption and has been widely adopted by the System-on-Chip (SoC) community. Yet, NoCs occupy more area and consume more power as the size of network increases. In this thesis, we propose a novel dynamic reconfigurable P2P (DRP2P) communication architecture for reconfigurable embedded systems, which is an alternative to the conventional NoC architectures. In DRP2P, interconnects are reconfigured on-the-fly as new communication requests arrive at the system. In embedded applications running on the multi-core systems, the traffic flow is usually known. Hence, DRP2P is very suitable for embedded systems. DRP2P is inspired from both P2P interconnects and NoC architecture. If the traffic flow is known in advance, it works as fast as P2P while reconfiguration process is done at the time of computation. Thus, next communication scenario can be established before communication starts. Since the reconfigurable wiring area in DRP2P is proportional to the network size, it is as scalable as NoC. In order to achieve reconfiguration efficiently, we developed three different dedicated self reconfiguration engines. The latest version of these engines is exploited in DRP2P architecture. DRP2P gives better results than conventional NoCs if the physical placement of cores on the embedded system is done properly by utilizing mapping and routing algorithms. Hence, fast and heuristic mapping and routing algorithms are also designed in the scope of this thesis. Experimental evaluations have shown that DRP2P outperforms conventional NoCs even in the worst case scenario as the amount of data in on-chip communication increases.

### ÖZET

# GÖMÜLÜ SİSTEMLER İÇİN YENİDEN BETİMLENEBİLİR YONGA ÜSTÜ AĞ (YüA) MİMARİLERİ

Noktadan noktaya (NN) ya da paylaşımlı veri yolu gibi haberleşme mimarileri, çekirdek sayısı ve bu çekirdekler arasındaki iletişim hacmi arttıkça ölçeklenememektedir. Güç tüketimini azaltmak için, Yonga-üstü-Ağ (YüA) mimarileri öne sürülmüş olup, bu mimariler Yonga-üstü-Sistem topluluğu tarafından yaygın olarak kabul görmüştür. Ancak ağ boyutu arttıkça, YüA mimarileri daha fazla alan kaplamakta ve daha çok güç tüketmektedirler. Bu yüzden, bu tezde, geleneksel YüA mimarilerine alternatif olarak, Dinamik Yeniden betimlenebilir Noktadan Noktaya (DYNN) mimariler sunulmaktadır. DYNN'de sisteme yeni haberleşme istekleri geldiğinde, bağlantılar dinamik olarak yeniden betimlenir. Çok çekirdekli sistemler üzerinde koşan Gömülü Sistem (GS) uygulamalarında, trafik akışı genellikle önceden bilinmektedir. DYNN mimarisi hem NN hem de YüA mimarilerinden esinlenerek tasarlanmıştır. Eğer trafik akışı önceden bilinirse, yeniden betimleme (YB) işlemi hesaplama zamanında yapıldığından, DYNN, NN kadar hızlı çalışır. Böylece, bir sonraki haberleşme senaryosu, haberleşme başlamadan kurulabilir. DYNN'de YB alanı ağ boyutu ile doğru orantılı olduğundan dolayı, DYNN, geleneksel YüA gibi ölçeklenebilmektedir. Etkin bir YB için, tez kapsamında üç adet YB motoru tasarlanmıştır. Bu motorların en son sürümü DYNN'de kullanılmış olup, hedef sistem tarafından desteklenen en yüksek hızda çalışabilmektedir. Eğer GS üzerinde çekirdeklerin yerleşmesi etkin eşleme ve yönlendirme algoritmaları kullanılarak yapılırsa, DYNN, geleneksel YüA'lardan daha iyi sonuçlar vermektedir. Bu yüzden, tez kapsamında sezgisel eşleme ve yönlendirme algoritmaları tasarlanmıştır. Deneysel sonuçlara göre, DYNN'nin yonga üstü haberleşmede verinin arttığı en kötü durumda bile, geleneksel YüA'dan daha iyi çalıştığı gözlemlenmiştir.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iv                                            |  |  |

|----------------------------------------------------------------|--|--|

| ABSTRACT                                                       |  |  |

| ÖZET                                                           |  |  |

| LIST OF FIGURES xi                                             |  |  |

| LIST OF TABLES                                                 |  |  |

| LIST OF SYMBOLS                                                |  |  |

| LIST OF ACRONYMS/ABBREVIATIONS                                 |  |  |

| 1. MOTIVATION                                                  |  |  |

| 2. THESIS OUTCOME                                              |  |  |

| 2.1. Key Contributions                                         |  |  |

| 2.2. Thesis Outline                                            |  |  |

| 3. DYNAMIC PARTIAL SELF-RECONFIGURATION (DPSR) ON XILINX FP-   |  |  |

| GAs 11                                                         |  |  |

| 3.1. Related Works on Self-Reconfigurable Systems              |  |  |

| 3.2. Related Works on Configuration Compression Techniques     |  |  |

| 4. A RECONFIGURATION ENGINE FOR LOW-COST FPGAs: PARALLEL       |  |  |

| CONFIGURATION ACCESS PORT (PCAP)                               |  |  |

| 4.1. PCAP Architecture                                         |  |  |

| 4.1.1. File Converter                                          |  |  |

| 4.1.2. Dynamic Partial Self-Reconfiguration Flow               |  |  |

| 4.2. Case Study: Run-Time DCM Reconfiguration                  |  |  |

| 5. A RECONFIGURATION ENGINE FOR COMPRESSED PARTIAL BITSTREAMS: |  |  |

| COMPRESSED PARALLEL CONFIGURATION ACCESS PORT (cPCAP) 31       |  |  |

| 5.1. cPCAP Architecture                                        |  |  |

| 5.1.1. File Compression and Conversion                         |  |  |

| 5.2. PCAP vs. cPCAP                                            |  |  |

| 6. A RECONFIGURATION ENGINE WITH INTERNAL CONFIGURATION        |  |  |

| INTERFACE: EXTENDED VERSION OF COMPRESSED PARALLEL CON-        |  |  |

| FIGURATION ACCESS PORT (cPCAPv2)                               |  |  |

|                                                            | 6.1.      | Config             | guration on Spartan-6 FPGAs                      | 36 |

|------------------------------------------------------------|-----------|--------------------|--------------------------------------------------|----|

|                                                            | 6.2.      | Self-Re            | econfiguration Platform                          | 38 |

|                                                            | 6.3.      | Test R             | Lesults                                          | 39 |

| 7.                                                         | AR        | ECONE              | FIGURATION ENGINE UTILIZING INTER-BITSTREAM COM- |    |

|                                                            | PRE       | SSION              | : DOUBLE COMPRESSED PARALLEL CONFIGURATION AC-   |    |

|                                                            | CES       | S POR              | $T(c^2PCAP)$                                     | 43 |

|                                                            | 7.1.      | c <sup>2</sup> PCA | P Configuration Flow                             | 43 |

|                                                            | 7.2.      | Comp               | ression                                          | 45 |

|                                                            |           | 7.2.1.             | Partial Bitstream Similarity Extraction          | 45 |

|                                                            |           | 7.2.2.             | Compression of Partial Bitstreams                | 46 |

|                                                            |           | 7.2.3.             | Selection of Optimal Compressed Bitstream Set    | 46 |

|                                                            |           | 7.2.4.             | Storage of Partial Bitstreams on Memory          | 49 |

|                                                            | 7.3.      | c <sup>2</sup> PCA | P Architecture                                   | 49 |

|                                                            | 7.4.      | Decon              | pression                                         | 52 |

|                                                            |           | 7.4.1.             | Look up table                                    | 52 |

|                                                            |           | 7.4.2.             | Decompressor                                     | 52 |

|                                                            |           | 7.4.3.             | Extractor                                        | 53 |

| 8.                                                         | MAI       | PPING,             | ROUTING PROBLEMS FOR NOC AND RECONFIGURABLE      |    |

|                                                            | INT       | ERCON              | NNECTS                                           | 54 |

|                                                            | 8.1.      | Relate             | d Works on NoC Mapping Problem                   | 56 |

|                                                            | 8.2.      | Relate             | d Works for NoC Routing Problem                  | 58 |

|                                                            | 8.3.      | Relate             | d Works for Reconfigurable Interconnects         | 61 |

| 9.                                                         | PAR       | TICLE              | FILTERING ALGORITHM FOR NoC MAPPING PROBLEM      | 63 |

|                                                            | 9.1.      | Propos             | sed Algorithm                                    | 65 |

|                                                            | 9.2.      | Case S             | Studies                                          | 75 |

|                                                            |           | 9.2.1.             | 2-D Regular Mesh Architectures                   | 77 |

|                                                            |           | 9.2.2.             | 2-D Irregular and Custom Mesh Architectures      | 80 |

|                                                            |           | 9.2.3.             | 3-D NoCs                                         | 84 |

|                                                            |           | 9.2.4.             | Large-Scale NoCs                                 | 87 |

|                                                            |           | 9.2.5.             | Scalability of PFMAP on 3-D NoCs                 | 90 |

| 10. SIMULTANEOUS MAPPING AND ROUTING FOR NoC WITH PARTICLE |           |                    |                                                  |    |

|                                                            | FILTERING |                    |                                                  |    |

| 10.1. Target Architecture and Main Objective of the Proposed Algorithm $$ .                                    | 94   |

|----------------------------------------------------------------------------------------------------------------|------|

| 10.2. Case Studies                                                                                             | 106  |

| 10.2.1. Comparison of PFROUT Routing performance with AppAw $[1]$                                              |      |

| on Synthetic Graphs from TGFF [2]                                                                              | 109  |

| 11. DYNAMIC RECONFIGURABLE POINT-TO-POINT INTERCONNECTS                                                        | 115  |

| 11.1. Proposed DRP2P Architecture                                                                              | 115  |

| 11.1.1. Theoretical Latency Analysis of DRP2P                                                                  | 117  |

| 11.1.2. Comparison of DRP2P with 2-D Mesh NoC                                                                  | 121  |

| 11.1.3. Comparison of DRP2P with a 2-D Reconfigurable Mesh NoC $[1]$                                           | 123  |

| 11.1.4. Comparison of DRP2P with other communication architectures                                             | 127  |

| 11.2. Design Flow for DRP2P                                                                                    | 128  |

| 11.2.1. Profiling of the Application                                                                           | 129  |

| 11.2.2. Partial Bitstream Generation for all Communication Scenarios $% \left( {{{\mathbf{r}}_{i}}} \right)$ . | 130  |

| 11.2.2.1. Dynamic Partial Self-Reconfiguration Flow                                                            | 130  |

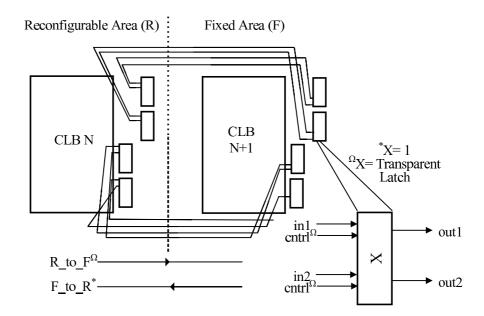

| 11.2.2.2. Slice Based Bus Macros                                                                               | 130  |

| 11.3. Test and Results                                                                                         | 131  |

| 11.3.1. Case Studies                                                                                           | 135  |

| 11.3.1.1. Target Tracking Application                                                                          | 135  |

| 11.3.1.2. N-Body Problem                                                                                       | 137  |

| 12. CONCLUSION                                                                                                 | 140  |

| 13. FUTURE DIRECTIONS                                                                                          | 143  |

| APPENDIX A: USER MANUAL FOR RECONFIGURATION ENGINES AND D                                                      | RP2P |

| 145                                                                                                            |      |

| A.1. Configuration Flow for Reconfiguration Engines                                                            | 146  |

| A.1.1. Dynamic Partial Self-Reconfiguration Flow                                                               | 147  |

| A.2. Partial Bitstream Manipulation                                                                            | 147  |

| A.2.1. Compression                                                                                             | 148  |

| A.2.1.1. Step 1: Partial Bitstream Extraction                                                                  | 148  |

| A.2.1.2. Step 2: Partial Bitstream Compression                                                                 | 149  |

| A.2.1.3. Step 3: Partial Bitstream Picking                                                                     | 150  |

| A.2.2. Decompression                                                                                           | 151  |

| A.2.2.1. Step 1: Partial Bitstream Decompression                                                               | 152  |

| A.2.2.2. Step 2: Partial Bitstream Extraction                                 | 152 |

|-------------------------------------------------------------------------------|-----|

| A.2.3. SelectMAP Specific Topics                                              | 152 |

| A.2.4. Internal Configuration Access Port (ICAP) Specific Topics $\ . \ .$    | 156 |

| A.2.5. Slice Based Bus Macros                                                 | 157 |

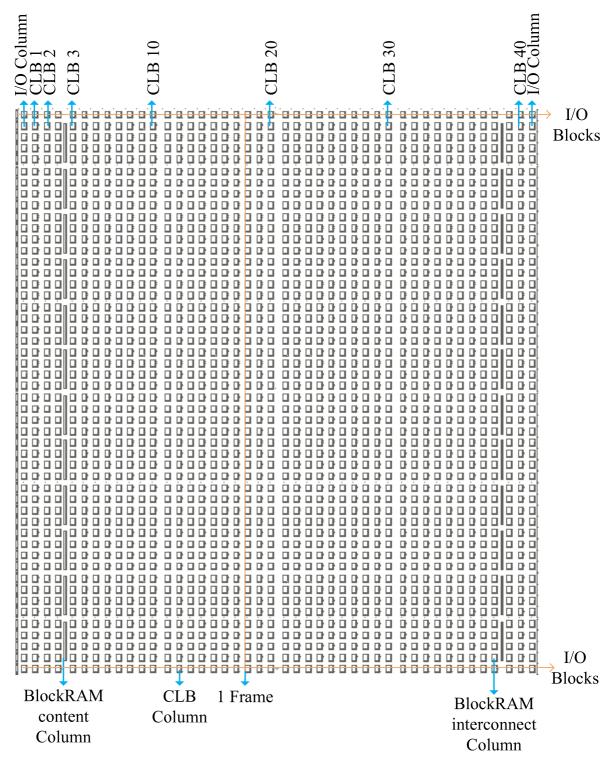

| A.3. The Configuration Architecture of Virtex-4 and Pure Spartan-III FPGAs $$ |     |

| from XILINX                                                                   | 159 |

| A.3.1. Creating Partial Reconfiguration Bitstreams                            | 165 |

| A.3.1.1. Difference-Based Partial Reconfiguration:                            | 165 |

| A.3.1.2g PartialMask Options of BitGen for Partial Reconfig-                  |     |

| uration:                                                                      | 168 |

| APPENDIX B: USER MANUAL FOR PFMAP                                             | 172 |

| APPENDIX C: USER MANUAL FOR PFROUT                                            | 177 |

| REFERENCES                                                                    | 181 |

### LIST OF FIGURES

| Figure 1.1. | MPEG2 application [3].                                                                        | 1  |

|-------------|-----------------------------------------------------------------------------------------------|----|

| Figure 1.2. | Possible on-chip communication architectures for MPEG2 applica-<br>tion [3].                  | 2  |

| Figure 1.3. | Computation, reconfiguration and communication periods in par-<br>tially DRP2P interconnects. | 3  |

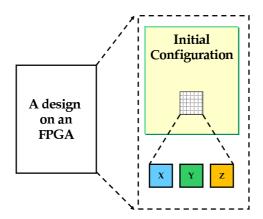

| Figure 1.4. | Pre-selected areas for partial reconfiguration.                                               | 4  |

| Figure 1.5. | Partial reconfiguration flow.                                                                 | 5  |

| Figure 1.6. | Dynamic partial reconfiguration.                                                              | 6  |

| Figure 1.7. | Dynamic partial self-reconfiguration.                                                         | 6  |

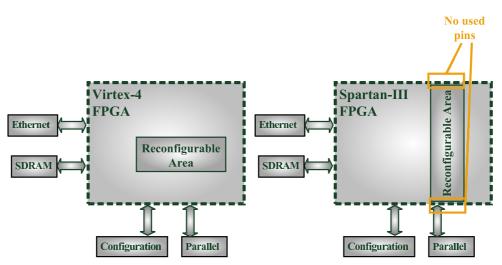

| Figure 4.1. | Possible reconfiguration areas in Virtex-4 and Spartan-3                                      | 23 |

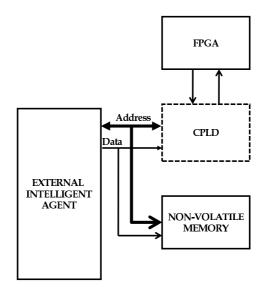

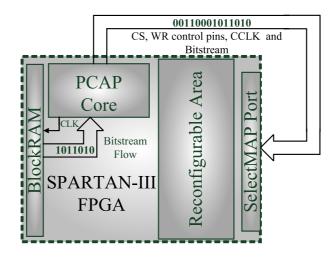

| Figure 4.2. | Hardware architecture of whole system with PCAP core. $\ . \ . \ .$ .                         | 24 |

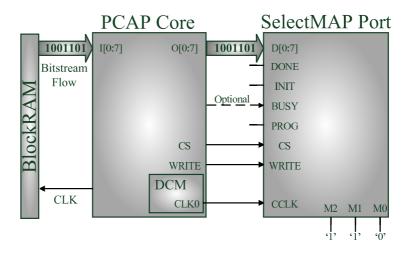

| Figure 4.3. | PCAP Core and SelectMAP interface.                                                            | 25 |

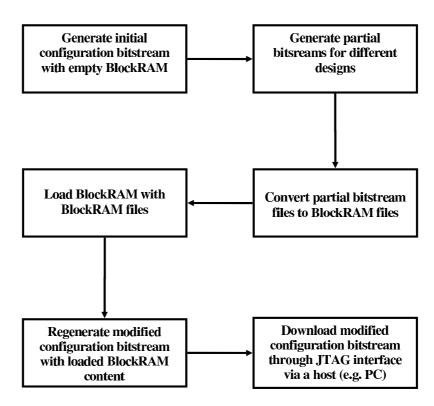

| Figure 4.4. | Configuration steps for PCAP core                                                             | 26 |

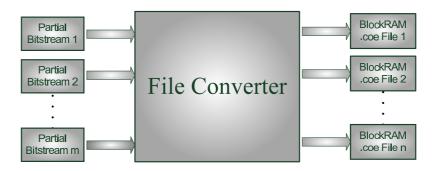

| Figure 4.5. | File conversion from partial bitstream file to BlockRAM coefficient         file.             | 27 |

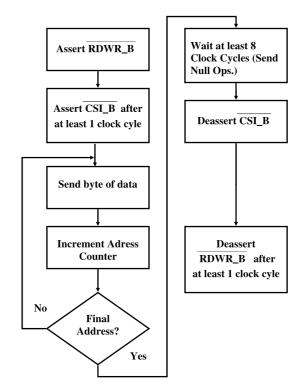

| Figure 4.6. | PCAP core configuration control flow diagram.                                                 | 27 |

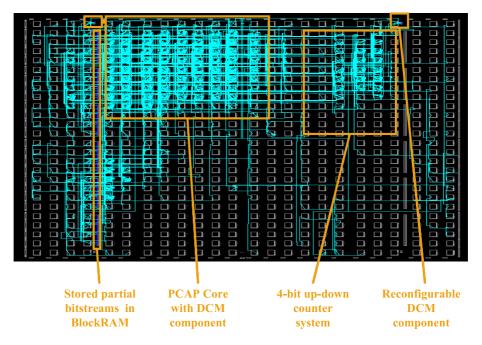

| Figure 4.7. | The complete system overview in FPGA Editor                                                                                                                       | 29 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

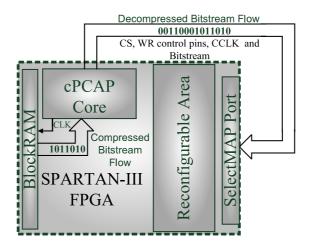

| Figure 5.1. | Hardware architecture of whole system with cPCAP core. $\ . \ . \ .$                                                                                              | 31 |

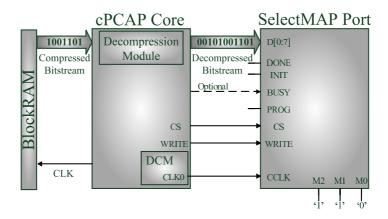

| Figure 5.2. | cPCAP Core and SelectMAP interface                                                                                                                                | 32 |

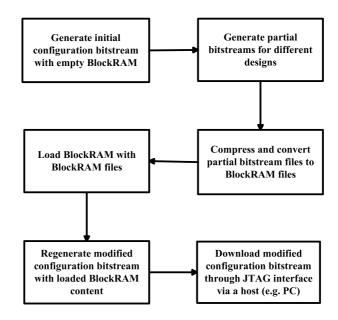

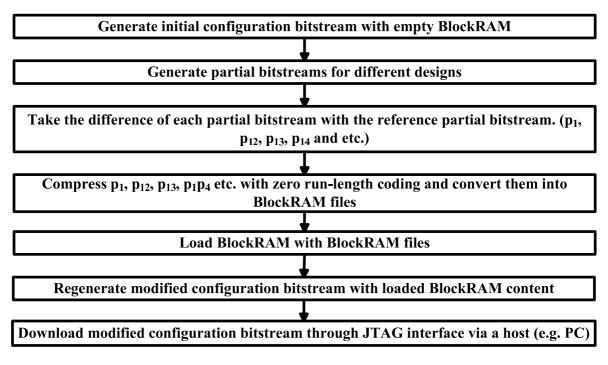

| Figure 5.3. | Configuration steps for cPCAP core                                                                                                                                | 33 |

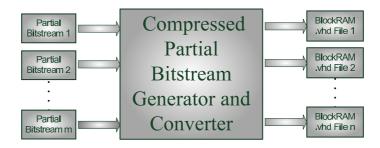

| Figure 5.4. | File conversion from partial bitstream file to BlockRAM coefficient      file.                                                                                    | 33 |

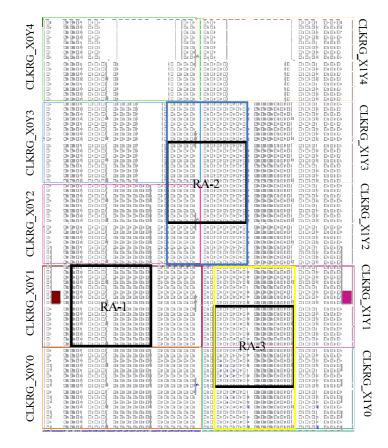

| Figure 6.1. | Selected reconfigurable areas on a Spartan-6 FPGA.                                                                                                                | 37 |

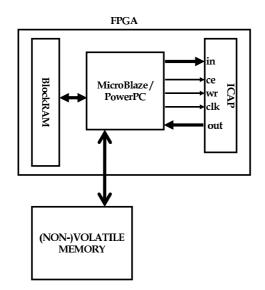

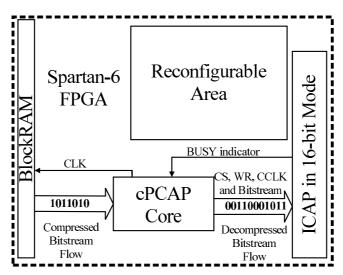

| Figure 6.2. | Hardware architecture of the system over internal configuration<br>port (ICAP) on a Spartan-6 FPGA.                                                               | 38 |

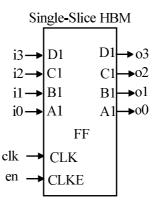

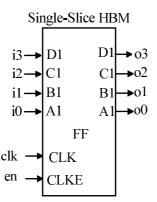

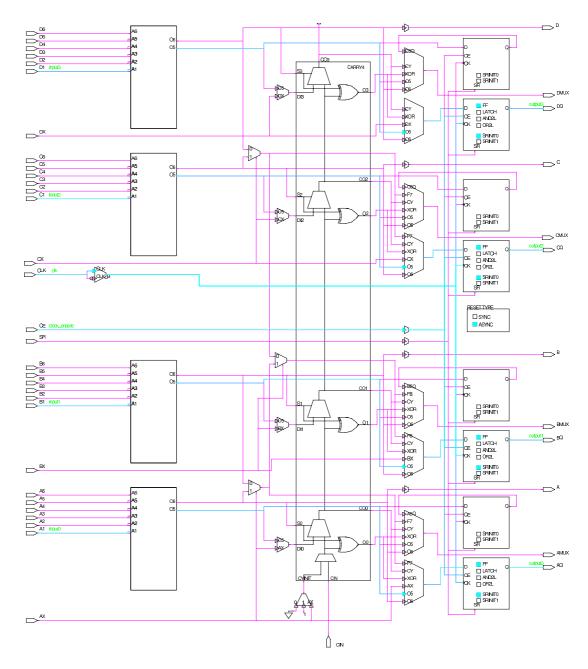

| Figure 6.3. | 4-bit single slice Spartan-6 HBM                                                                                                                                  | 39 |

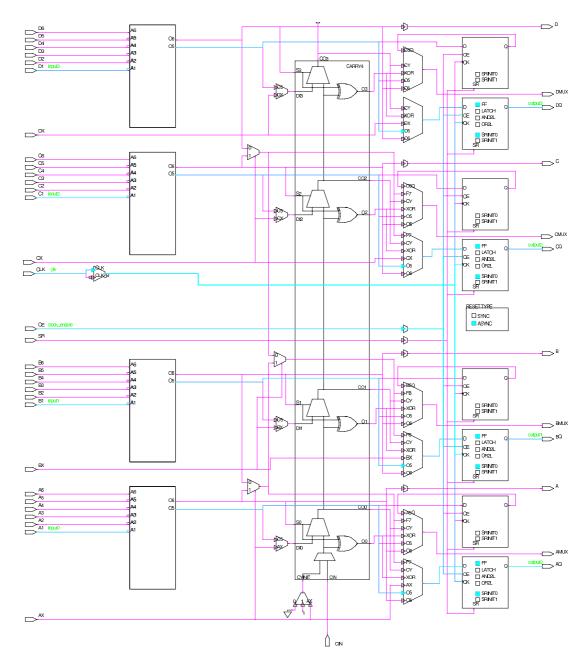

| Figure 6.4. | Inside of Spartan-6 slice based HBM                                                                                                                               | 40 |

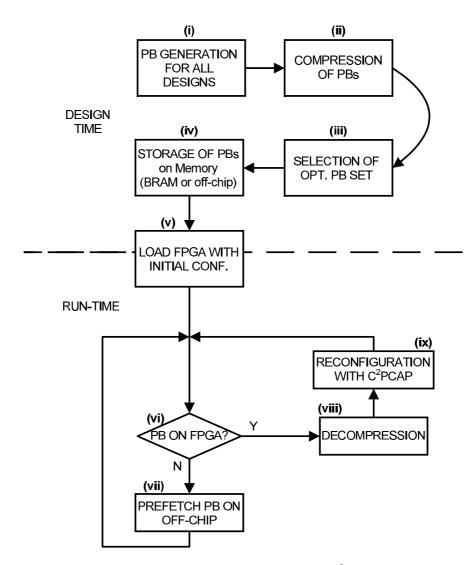

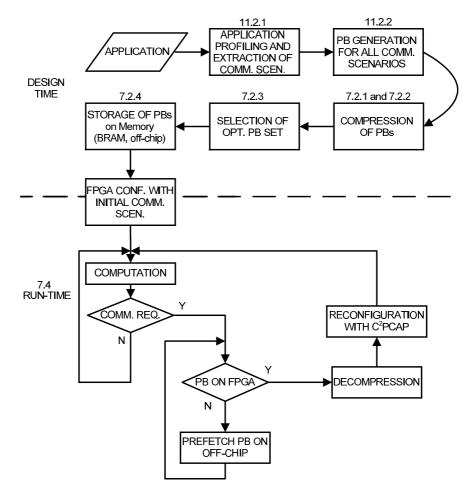

| Figure 7.1. | Configuration steps for $c^2$ PCAP                                                                                                                                | 44 |

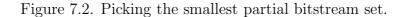

| Figure 7.2. | Picking the smallest partial bitstream set.                                                                                                                       | 48 |

| Figure 7.3. | Steps of the bitstream set selection algorithm (Figure 7.2) for an eight-core implementation on a Virtex-4 FPGA. (X = XOR, if $i \neq j$ ; X = AND, if $i = j$ ). | 49 |

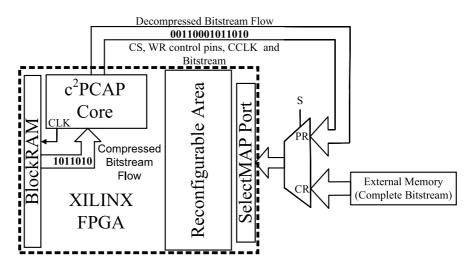

| Figure 7.4. | Hardware architecture of the system over external configuration port.                                                                                             | 50 |

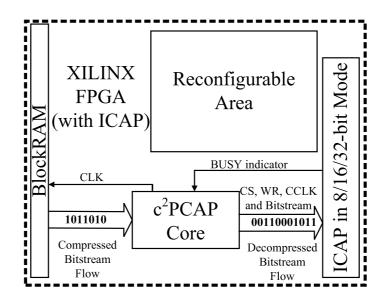

| Figure 7.5.  | Hardware architecture of the system over internal configuration port                                                                       | 51 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

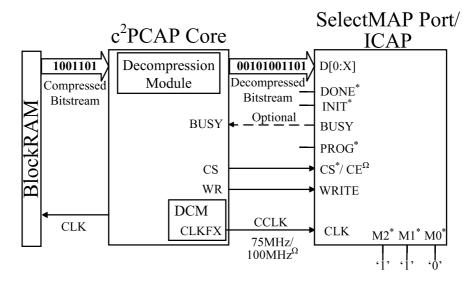

| Figure 7.6.  | $c^2$ PCAP core and SelectMAP/ ICAP interfaces(X:7/15/31, *: only for SelectMAP, $\Omega$ :only for ICAP).                                 | 51 |

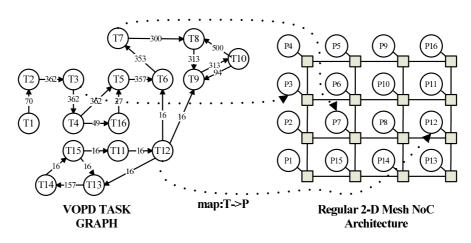

| Figure 9.1.  | Task mapping process on a regular 2-D Mesh NoC.                                                                                            | 63 |

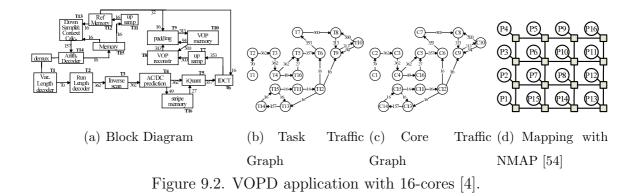

| Figure 9.2.  | VOPD application with 16-cores [4].                                                                                                        | 66 |

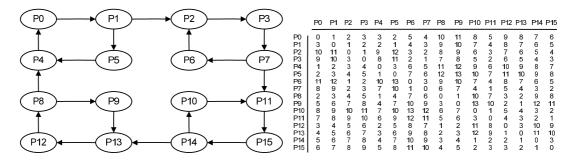

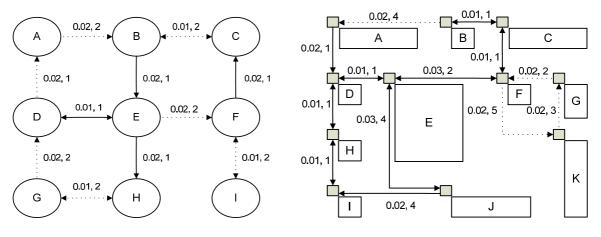

| Figure 9.3.  | An irregular processor communication topology and it's distance matrix.                                                                    | 69 |

| Figure 9.4.  | Main part of configuration mapping algorithm.                                                                                              | 70 |

| Figure 9.5.  | Random configuration function.                                                                                                             | 71 |

| Figure 9.6.  | Random swap node pair function                                                                                                             | 72 |

| Figure 9.7.  | Re-sample particles systematically.                                                                                                        | 73 |

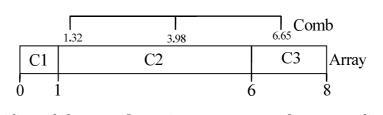

| Figure 9.8.  | Residing of three configurations on an array for re-sampling step<br>by using comb.                                                        | 75 |

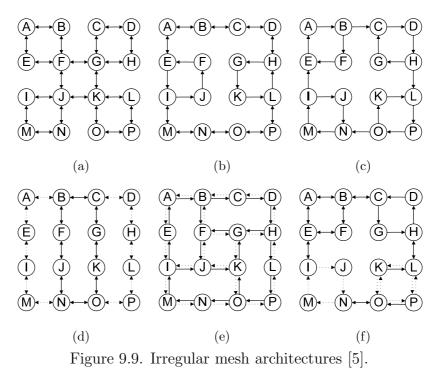

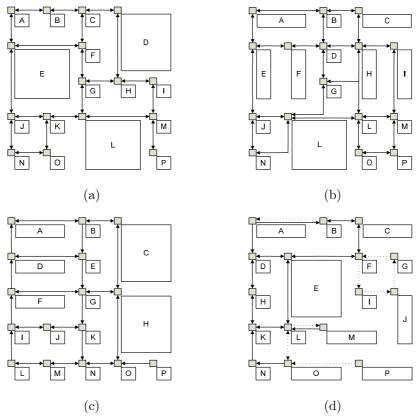

| Figure 9.9.  | Irregular mesh architectures [5]                                                                                                           | 78 |

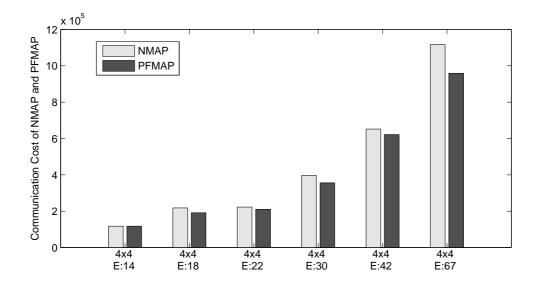

| Figure 9.10. | Communication cost comparison of PFMAP and NMAP on a 2-D NoC with fixed size (4x4) with increasing communication demand.                   | 79 |

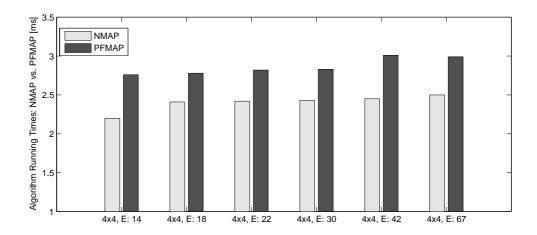

| Figure 9.11. | Algorithm running time of NMAP and PFMAP on a 2-D NoC with fixed size (4x4) with increasing communication demand (IT=10, PN=10 for PFMAP). | 80 |

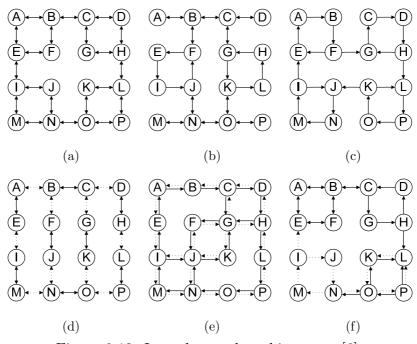

| Figure 9.12. | Irregular mesh architectures [6]                                                                                    | 80 |

|--------------|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 9.13. | Custom mesh architectures [6]                                                                                       | 81 |

| Figure 9.14. | Energy, latency representation of irregular and custom architec-<br>tures.                                          | 83 |

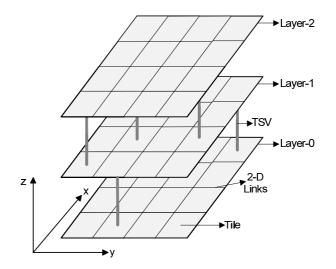

| Figure 9.15. | A 3-D NoC architecture with the size of 4x4x3.                                                                      | 85 |

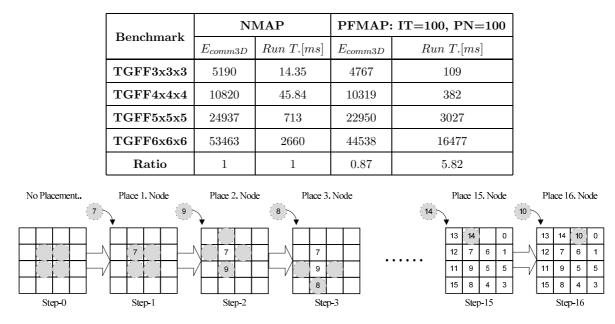

| Figure 9.16. | Determine X, Y, Z dimensions for 3-D NoC                                                                            | 86 |

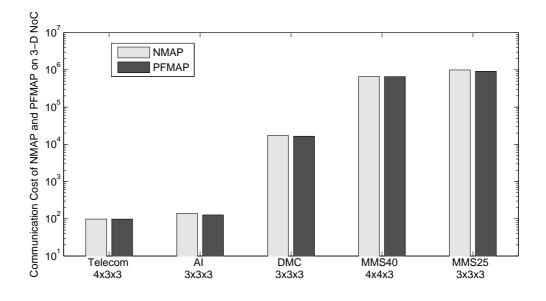

| Figure 9.17. | Communication cost of PFMAP and NMAP on a 3-D NoC                                                                   | 86 |

| Figure 9.18. | PFMAP initialization steps for large-scale NoCs                                                                     | 88 |

| Figure 9.19. | Initialization function.                                                                                            | 89 |

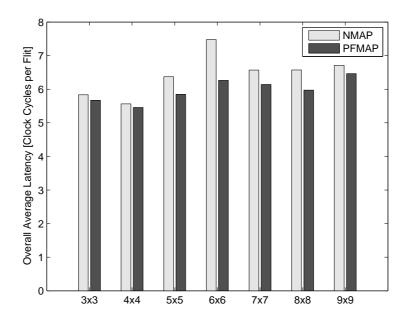

| Figure 9.20. | Average network latency comparison of NMAP and PFMAP for different size of synthetic task graphs.                   | 90 |

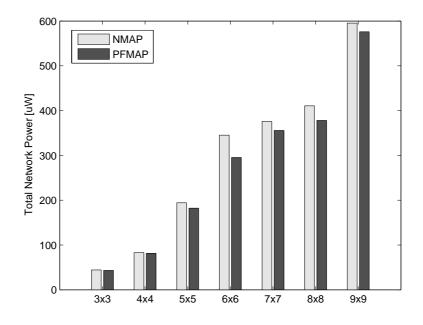

| Figure 9.21. | Total network power comparison of NMAP and PFMAP for differ-<br>ent size of synthetic task graphs.                  | 91 |

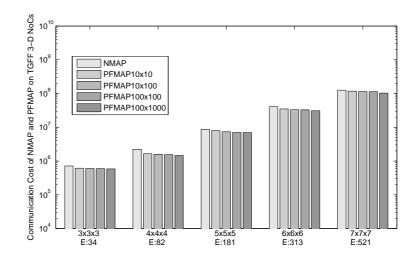

| Figure 9.22. | Communication cost of PFMAP and NMAP algorithms on 3-D<br>NoC for different size of TGFF applications.              | 92 |

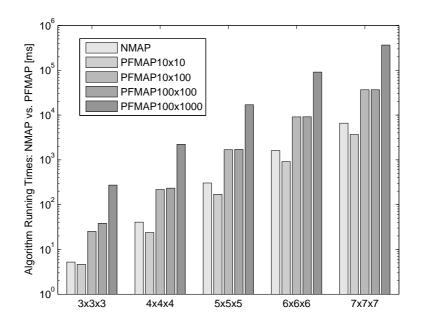

| Figure 9.23. | Running time of NMAP and PFMAP algorithms with different size of IT and PN for different size of TGFF applications. | 92 |

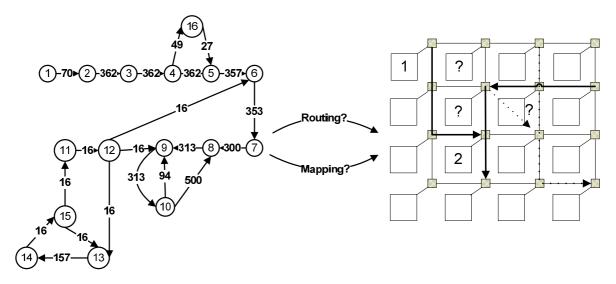

| Figure 10.1. | Mapping and routing of an application onto a 2-D mesh NoC ar-<br>chitecture.                                        | 93 |

xiv

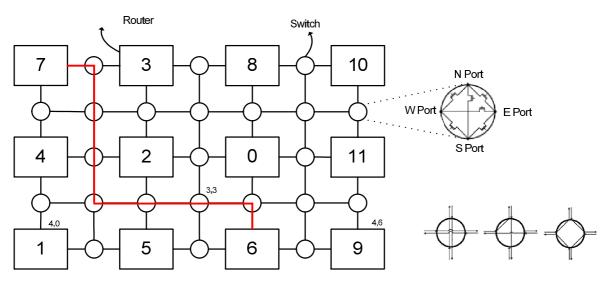

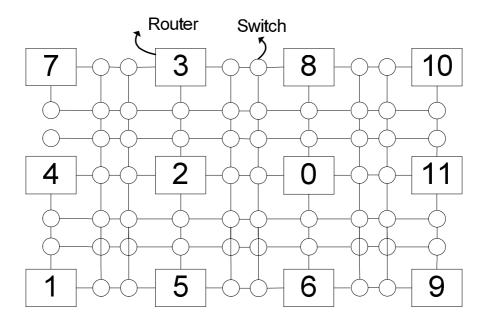

| Figure 10.2.  | 2-D reconfigurable NoC architecture with corridor width one (i.e. CW=1) [1]                                                       | 95  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 10.3.  | 2-D reconfigurable NoC architecture with corridor width two (i.e. CW=2) [1]                                                       | 97  |

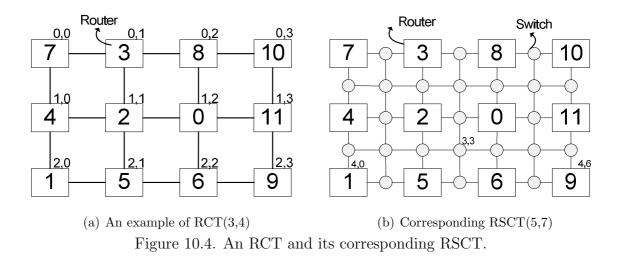

| Figure 10.4.  | An RCT and its corresponding RSCT.                                                                                                | 98  |

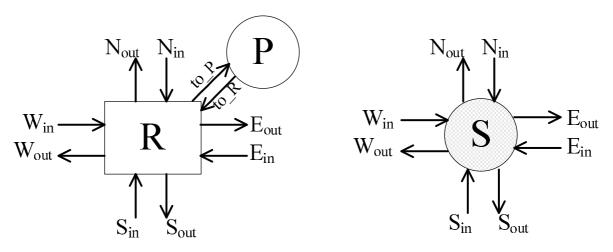

| Figure 10.5.  | Number of available maximum inputs and output for router/switch.                                                                  | 98  |

| Figure 10.6.  | Main part of PFROUT algorithm.                                                                                                    | 100 |

| Figure 10.7.  | Configuration routing algorithm.                                                                                                  | 102 |

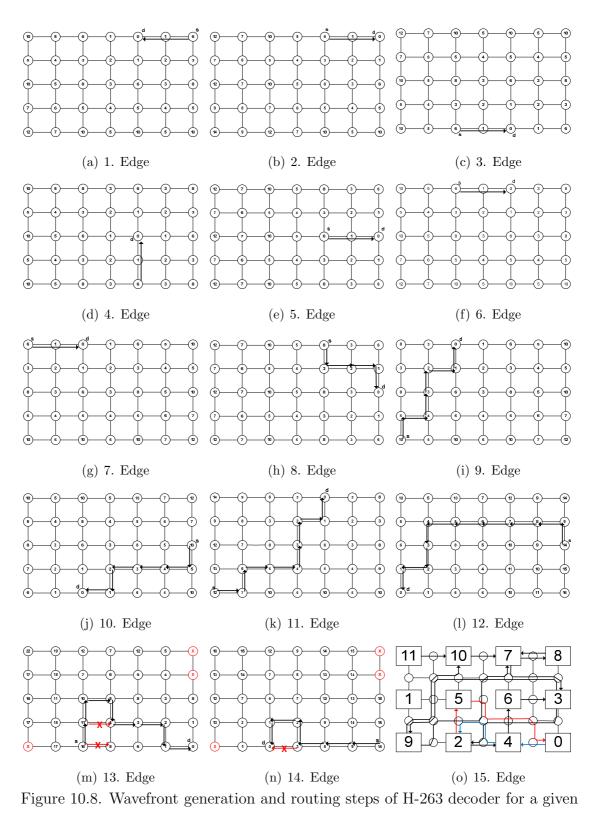

| Figure 10.8.  | Wavefront generation and routing steps of H-263 decoder for a given configuration.                                                | 103 |

| Figure 10.9.  | Routing of single path                                                                                                            | 104 |

| Figure 10.10. | Nodes neighbourhood function.                                                                                                     | 105 |

| Figure 10.11. | Search for shared paths.                                                                                                          | 105 |

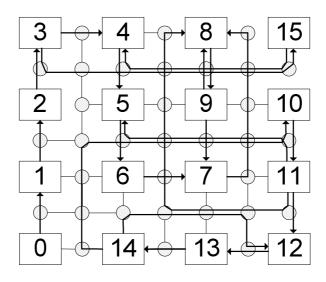

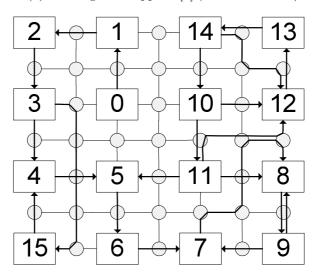

| Figure 10.12. | Routing of VOPD application with AppAw [1], PFMAP [7] and PFROUT for CW=1.                                                        | 107 |

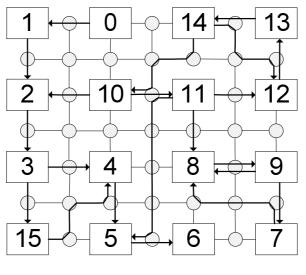

| Figure 10.13. | Total (shared and non-shared) and direct (non-shared) solution percentages of synthetic task graphs from $3x3$ to $10x10$ (TGFF). | 110 |

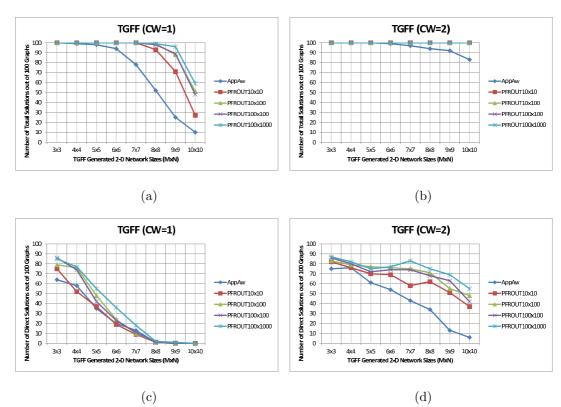

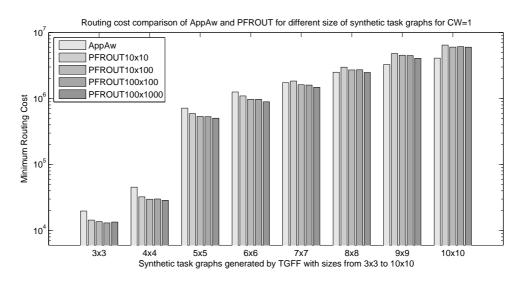

| Figure 10.14. | Minimum routing cost values of both PFROUT and AppAw [1] algorithms on various networks for CW=1.                                 | 111 |

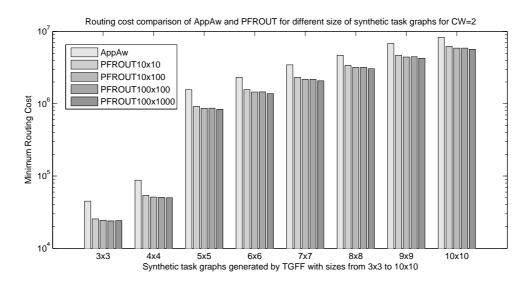

| Figure 10.15 | Minimum routing cost values of both PFROUT and AppAw [1] algorithms on various networks for CW=2.               | 112 |

|--------------|-----------------------------------------------------------------------------------------------------------------|-----|

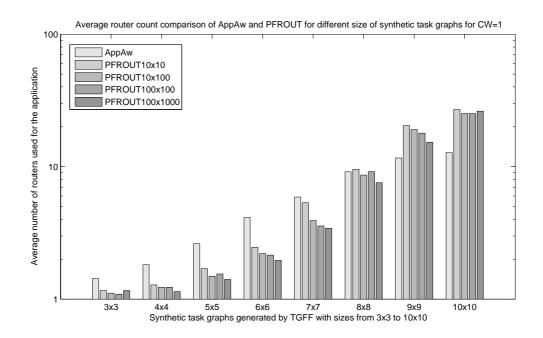

| Figure 10.16 | Average number of routers used for both PFROUT and AppAw [1] algorithms on various networks for CW=1.           | 112 |

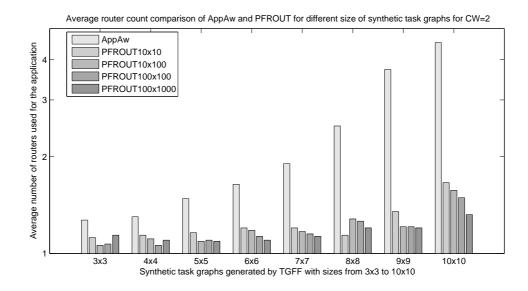

| Figure 10.17 | Average number of routers used for both PFROUT and AppAw [1] algorithms on various networks for CW=2.           | 113 |

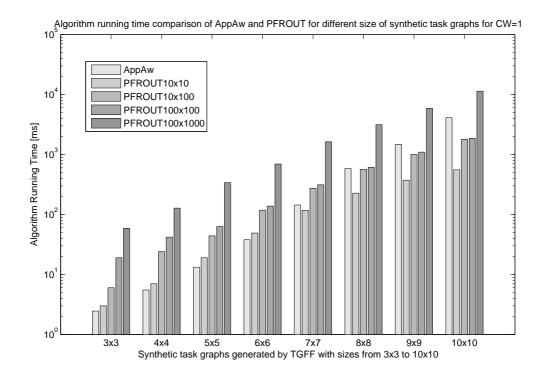

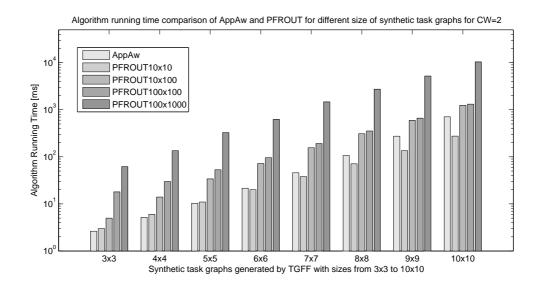

| Figure 10.18 | Comparison of algorithm running times of both PFROUT and Ap-<br>pAw [1] algorithms on various networks for CW=1 | 114 |

| Figure 10.19 | Comparison of algorithm running times of both PFROUT and Ap-<br>pAw [1] algorithms on various networks for CW=2 | 114 |

| Figure 11.1. | Different P ( $\#$ of partial bitstreams) values that can be stored in the BRAM on Virtex-4 FPGAs               | 116 |

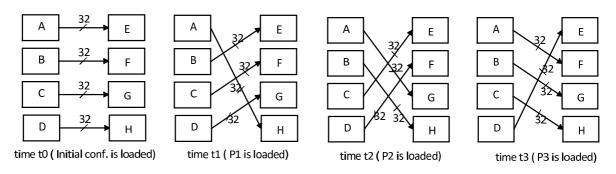

| Figure 11.2. | Four different communication scenarios.                                                                         | 118 |

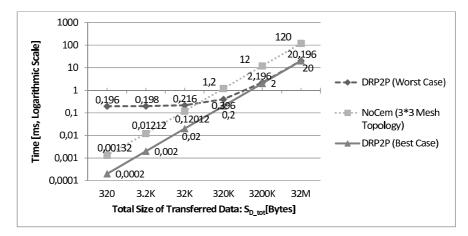

| Figure 11.3. | Comparison of DRP2P and NoCem with $3^*3$ mesh topology for different $S_D$ values                              | 121 |

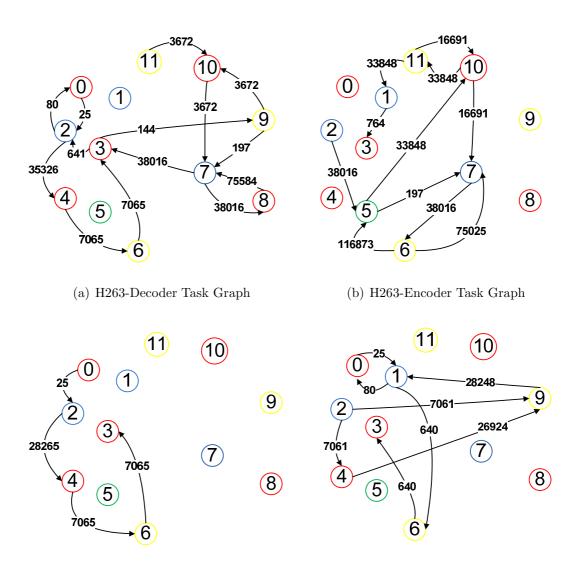

| Figure 11.4. | Task graphs of applications in MMS suite.                                                                       | 125 |

| Figure 11.5. | MMS physical placement on FPGA.                                                                                 | 126 |

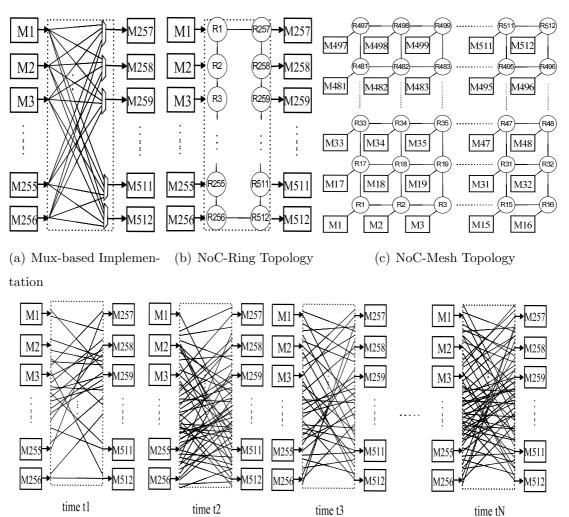

| Figure 11.6. | n-bit width k*k (k=256) point communication architecture and possible implementations. $\ldots$                 | 127 |

| Figure 11.7. | Design flow for DRP2P.                                                                                          | 129 |

| Figure 11.8.  | General structure of slice based bus macros.                                                                                                      | 131 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

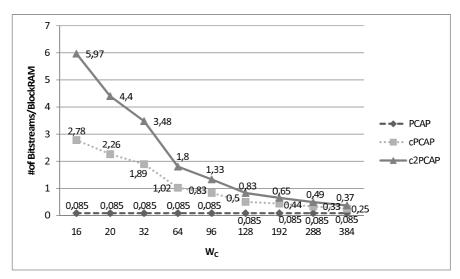

| Figure 11.9.  | # of bitstreams per BRAM vs. $W_C$ for communication reconfigu-<br>ration of PCAP [8], cPCAP [9] and $c^2$ PCAP cores                             | 134 |

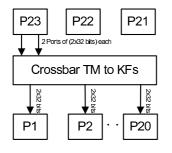

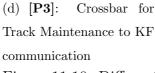

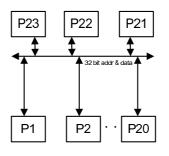

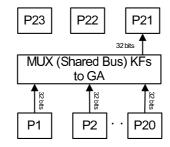

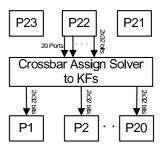

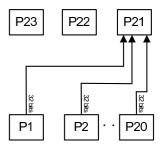

| Figure 11.10. | . Different scenarios of MPSoC architecture for MTT in a PRT                                                                                      | 136 |

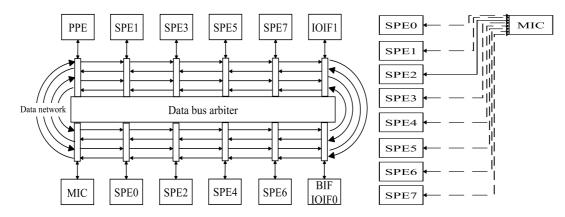

| Figure 11.11. | Element interconnect bus (EIB) and DRP2P communication be-<br>tween SPEs and MIC.                                                                 | 138 |

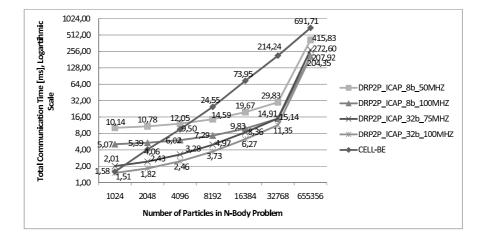

| Figure 11.12. | Total time consumed for communication between SPEs in N-Body problem with different number of particles.                                          | 139 |

| Figure A.1.   | Configuration flow.                                                                                                                               | 146 |

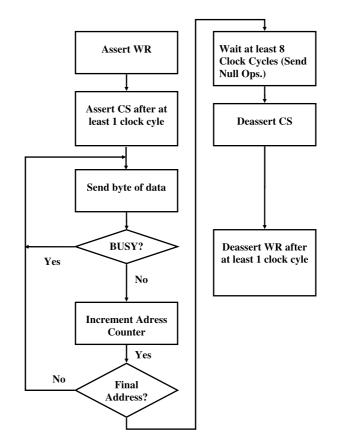

| Figure A.2.   | $c^2$ PCAP core configuration control flow diagram                                                                                                | 147 |

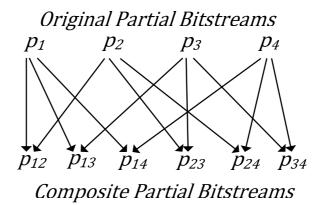

| Figure A.3.   | Possible composite partial bitstreams, N=4                                                                                                        | 149 |

| Figure A.4.   | Bitstream compression example with zero run-length encoding                                                                                       | 150 |

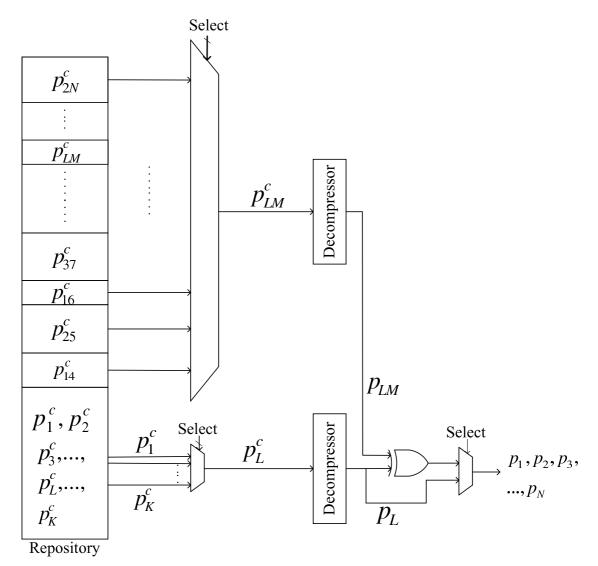

| Figure A.5.   | Decompressing and extracting original bitstreams in two steps (PR:<br>Any reference bitstream, N: $\#$ of original bitstreams, M<=N, K<=N, L<=K). |     |

| Figure A.6.   | Spartan-3 starter kit board expansion connectors [10]                                                                                             | 154 |

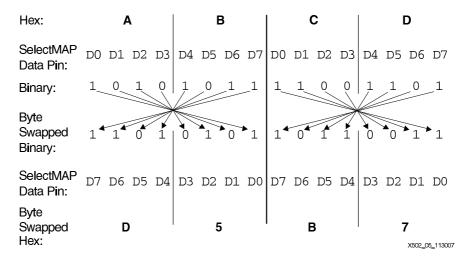

| Figure A.7.   | Byte-Swapping Example [10].                                                                                                                       | 154 |

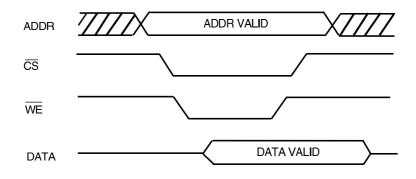

| Figure A.8.   | Write cycle timing diagram [10].                                                                                                                  | 156 |

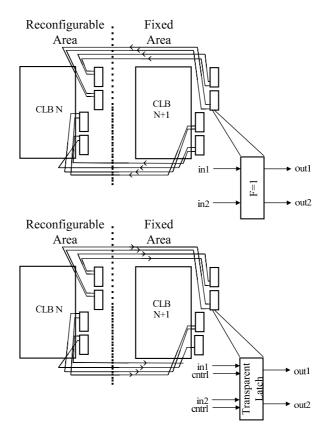

| Figure A.9.   | General structure of slice based bus macro.                                                                                                       | 158 |

| Figure A.10. | 4-bit single slice Spartan-6 HBM                                                           | 159 |

|--------------|--------------------------------------------------------------------------------------------|-----|

| Figure A.11. | Inside of Spartan-6 slice based HBM                                                        | 160 |

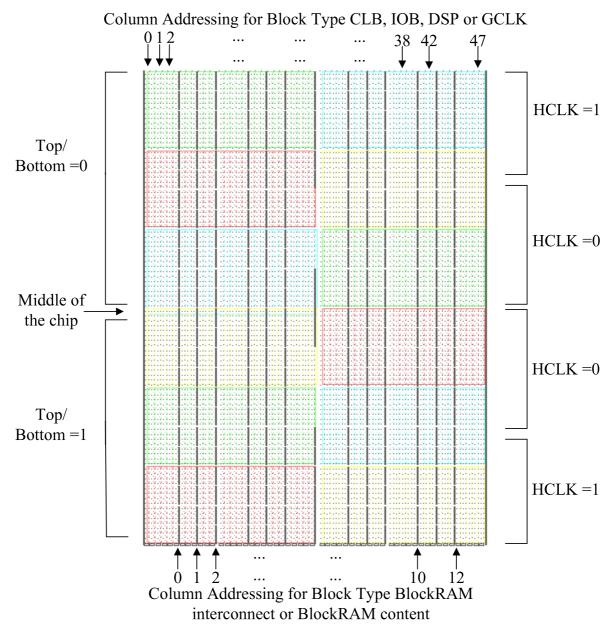

| Figure A.12. | Virtex-4 configuration frame addressing scheme [11]                                        | 161 |

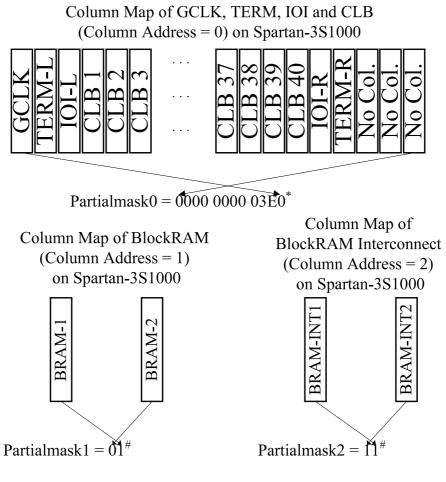

| Figure A.13. | Configuration column addressing scheme for Spartan-3S1000 FPGA.                            | 162 |

| Figure A.14. | Partial mask derivation example for Spartan-3S1000 FPGA. $\ . \ .$ .                       | 164 |

| Figure A.15. | -g Persist:yes setting for initial bitstream (SelectMAP)                                   | 167 |

| Figure A.16. | Defining a PAR guide design file.                                                          | 169 |

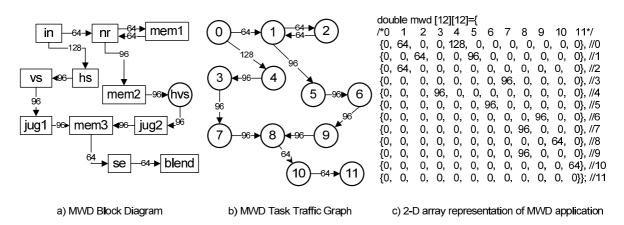

| Figure B.1.  | MWD application for PFMAP algorithm.                                                       | 172 |

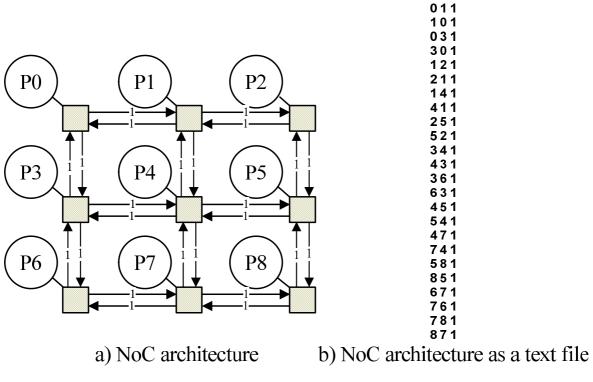

| Figure B.2.  | A 2-D mesh 3x3 NoC architecture and its representation as a text file for PFMAP algorithm. | 173 |

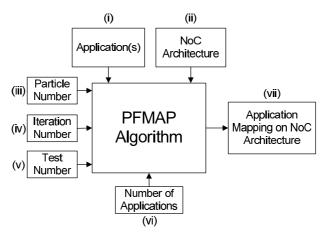

| Figure B.3.  | Inputs and outputs of the PFMAP algorithm.                                                 | 173 |

| Figure B.4.  | PFMAP output text file for MWD application.                                                | 176 |

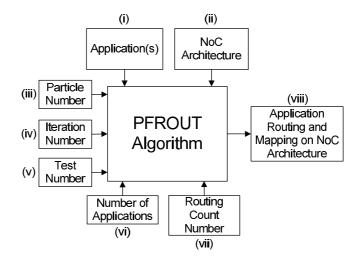

| Figure C.1.  | Inputs and outputs of the PFROUT algorithm.                                                | 177 |

| Figure C.2.  | PFROUT output text file for a synthetic TGFF3x3 application for CW=1.                      | 179 |

### LIST OF TABLES

| Table 3.1. | A summary of some previous works on self-reconfigurable systems.                                                                   | 18 |

|------------|------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2. | A summary of some previous studies on configuration compression<br>techniques.                                                     | 20 |

| Table 4.1. | FPGA resources.                                                                                                                    | 29 |

| Table 5.1. | Occupied resources for PCAP and cPCAP cores.                                                                                       | 34 |

| Table 6.1. | PB sizes and reconfiguration times for forward counter example.                                                                    | 39 |

| Table 6.2. | PB sizes and reconfiguration times for HBM tester example. $\ . \ .$                                                               | 41 |

| Table 7.1. | A sample Look Up Table $(I^s = \{1,3,\{23\},\{34\}\}, ADR_{p_1}: address$<br>of $p_1^c$ , $ADR_{p_{23}}: address$ of $p_{23}^c$ ). | 53 |

| Table 8.1. | Comparison of latest NoC approaches.                                                                                               | 59 |

| Table 9.1. | Algorithm running time and communication cost results of PFMAP<br>on different applications.                                       | 76 |

| Table 9.2. | Algorithm running time and communication cost results of various studies.                                                          | 77 |

| Table 9.3. | Communication cost of VOPD application on six different irregular mesh architectures (4x4).                                        | 82 |

| Table 9.4. | Communication Cost of VOPD application on four different custom mesh architectures (4x4).                                          | 82 |

| Table 9.5.  | Total travel distance (wirelength) by all packets                                                                      | 82  |

|-------------|------------------------------------------------------------------------------------------------------------------------|-----|

| Table 9.6.  | Communication energy and latency comparison of NMAP and PFMA<br>on both irregular and custom architectures.            |     |

| Table 9.7.  | Communication energy comparison of NMAP and PFMAP on 3-D<br>NoCs                                                       | 88  |

| Table 10.1. | Routing cost comparison of AppAw [1], PFMAP [7] and PFROUT<br>on MMS-Suite application.                                | 108 |

| Table 10.2. | Routing cost comparison of AppAw [1], PFMAP [7] and PFROUT<br>on MWD, VOPD and DMC applications.                       | 109 |

| Table 11.1. | Power Consumption of ML402 board and occupied area on Virtex-<br>4SX35 and Spartan-6 XC6SLX45, 8-Modules ( $W_C$ :128) | 123 |

| Table 11.2. | Partial bitstream size and their compression ratios for communica-<br>tion reconfiguration on Spartan-3 1000 FPGA.     | 133 |

| Table 11.3. | Partial bitstream storage cost of communication reconfiguration for<br>PCAP [8], cPCAP [9] and $c^2$ PCAP cores        | 134 |

| Table 11.4. | Reconfiguration latencies[ms] for case studies.                                                                        | 137 |

| Table A.1.  | SelectMAP port pin descriptions.                                                                                       | 152 |

| Table A.2.  | Loopback hardware pin connections for SelectMAP port on Spartan-<br>3 starter kit board                                | 153 |

| Table A.3.  | Loopback hardware byte swapping for SelectMAP port on Spartan-<br>3 starter kit board.                                 | 155 |

| Table A 4  | Spartan-3 bitstream column types |    | 'n |

|------------|----------------------------------|----|----|

| Table A.4. | spartan-5 busilean column types. | 11 | υ  |

## LIST OF SYMBOLS

| $ADR_{p_i}$         | Address of $p_i^c$                                                    |

|---------------------|-----------------------------------------------------------------------|

| C                   | Computational core set/ Number of columns in a regular 2-D            |

|                     | mesh NoC architecture                                                 |

| С                   | Vertical index of a node in regular 2-D mesh NoC architecture         |

| $CC_{se}$           | Communication cost for a single edge                                  |

| $dist_{i,j}$        | Dijkstra's shortest path                                              |

| $E_{bit}^{t_i,t_j}$ | Average energy consumption of sending one bit of data from            |

|                     | one node to another node                                              |

| $E_{comm}$          | Total communication energy                                            |

| $E_{LHbit}$         | Energy consumed on horizontal links                                   |

| $E_{LVbit}$         | Energy consumed on vertical links                                     |

| $E_{L_{bit}}$       | Energy consumed by switches between tiles                             |

| $E_{Rbit}$          | Energy consumed by a router                                           |

| $E_{S_{bit}}$       | Energy consumed by switches between tiles                             |

| $f_{i,j}$           | Traffic flow from node $i$ to node $j$                                |

| $G_x$               | Subset of $I^S$ and it contains partial bitstreams $p_i$ that have    |

|                     | to be stored in BRAM                                                  |

| $I^S$               | Optimal set with $N$ compressed bitstreams                            |

| i                   | Threshold value                                                       |

| $K_m$               | The set of all subsets with $m$ members from $I$                      |

| $L_{comm}$          | Total communication latency                                           |

| $l_{i,j}$           | Link between cores $c_i$ and $c_j$                                    |

| $l_{ij}$            | Length of joint partial bitstream of $i^{th}$ and $j^{th}$ bitstreams |

| $l_i$               | Length of $i^{th}$ partial bitstream                                  |

| MDist               | Manhattan Distance                                                    |

| N                   | Number of communication scenarios/ Number of task nodes               |

| n                   | Number of routers                                                     |

| $n_{hops}$          | Number of hops                                                        |

| $n_H$               | Number of horizontal links                                            |

| $n_V$ Number of vertical links $P$ Number of physical processors $p_{ij}$ Joint bitstream of $p_i$ and $p_j$ $p_{ij}^c$ Compressed version of joint partial bitstream $p_{ij}$ $p_i$ Partial bitstream that is generated by reconfiguration of a<br>region $p_i^c$ Compressed version of partial bitstream $p_i$ $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Computation time $T_{comp}$ Computation time $t_{i,j}$ Taffic amount from node $i$ to node $j$ $t_i$ Tile $i$ $T_{reconf}$ Reconfiguration time | $n_i$        | $i^{th}$ task node                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------|

| $p_{ij}$ Joint bitstream of $p_i$ and $p_j$ $p_{ij}^c$ Compressed version of joint partial bitstream $p_{ij}$ $p_i$ Partial bitstream that is generated by reconfiguration of a<br>region $p_i^c$ Compressed version of partial bitstream $p_i$ $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Communication time $T_{comm}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                       | $n_V$        | Number of vertical links                                        |

| $p_{ij}^c$ Compressed version of joint partial bitstream $p_{ij}$ $p_i$ Partial bitstream that is generated by reconfiguration of a<br>region $p_i^c$ Compressed version of partial bitstream $p_i$ $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Computation time $T_{comm}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                     | Р            | Number of physical processors                                   |

| $p_i$ Partial bitstream that is generated by reconfiguration of a<br>region $p_i^c$ Compressed version of partial bitstream $p_i$ $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Communication time $T_{comm}$ Computation time $t_{i,j}$ Taffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                      | $p_{ij}$     | Joint bits<br>tream of $p_i$ and $p_j$                          |

| region $p_i^c$ Compressed version of partial bitstream $p_i$ $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Computation time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                            | $p_{ij}^c$   | Compressed version of joint partial bitstream $p_{ij}$          |

| $p_i^c$ Compressed version of partial bitstream $p_i$ $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                 | $p_i$        | Partial bitstream that is generated by reconfiguration of a     |

| $p_j$ Partial bitstream that is generated by reconfiguration of the<br>same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Cycle time of the system clock $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                           |              | region                                                          |

| $P_{r,c}$ same region with $p_i$ after a period of time $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Computation time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                             | $p_i^c$      | Compressed version of partial bitstream $p_i$                   |

| $P_{r,c}$ Physical location of a processor with row index $r$ and column<br>index $c$ $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{comm}$ Cycle time of the system clock $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                | $p_j$        | Partial bitstream that is generated by reconfiguration of the   |

| index $c$ rHorizontal index of a node in regular 2-D mesh NoC<br>architectureRNumber of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer sizeTNumber of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | same region with $p_i$ after a period of time                   |

| $r$ Horizontal index of a node in regular 2-D mesh NoC<br>architecture $R$ Number of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $P_{r,c}$    | Physical location of a processor with row index $r$ and column  |

| $R$ architecture $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | index $c$                                                       |

| RNumber of rows in a regular 2-D mesh NoC architecture $S_D$ Data transfer sizeTNumber of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | r            | Horizontal index of a node in regular 2-D mesh NoC              |

| $S_D$ Data transfer size $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | architecture                                                    |

| $T$ Number of non-zero directed edges between nodes $n_i$ and $n_j$ $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R            | Number of rows in a regular 2-D mesh NoC architecture           |

| $T_{clk}$ Cycle time of the system clock $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $S_D$        | Data transfer size                                              |

| $T_{comm}$ Communication time $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T            | Number of non-zero directed edges between nodes $n_i$ and $n_j$ |

| $T_{comp}$ Computation time $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $T_{clk}$    | Cycle time of the system clock                                  |

| $t_{i,j}$ Traffic amount from node $i$ to node $j$ $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $T_{comm}$   | Communication time                                              |

| $t_i$ Tile $i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $T_{comp}$   | Computation time                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $t_{i,j}$    | Traffic amount from node $i$ to node $j$                        |

| $T_{reconf}$ Reconfiguration time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $t_i$        | Tile <i>i</i>                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $T_{reconf}$ | Reconfiguration time                                            |

| $W_c$ Channel width between modules (in bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $W_c$        | Channel width between modules (in bits)                         |

# LIST OF ACRONYMS/ABBREVIATIONS

| AI    | Automotive Industry                                     |

|-------|---------------------------------------------------------|

| APU   | Accelerated Processing Unit                             |

| ASP2P | Application Specific Point to Point                     |

| BRAM  | Block RAM                                               |

| BB    | Branch-and-Bound                                        |

| BM    | Bus Macro                                               |

| CCLK  | Configuration Clock                                     |

| CLB   | Configurable Logic Block                                |

| cPCAP | compressed Parallel Configuration Access Port           |

| CPLD  | Complex Programmable Logic Device                       |

| CR    | Complete Reconfiguration/Compression Ratio/Clock Region |

| CS    | Compressed Size                                         |

| CTG   | Core Traffic Graph                                      |

| DCM   | Digital Clock Manager                                   |

| DMA   | Direct Memory Access                                    |

| DPSR  | Dynamic Partial Self-Reconfiguration                    |

| DPT   | State Planning Organization of Turkey                   |

| DRP   | Dynamic Reconfiguration Port                            |

| DRP2P | Dynamically Reconfigurable Point to Point Interconnects |

| DSD   | Dual Screen Display                                     |

| DTCNN | Discrete Time Cellular Neural Network                   |

| DyNoC | Dynamic Network on Chip                                 |

| E3S   | Embedded Systems Synthesis Benchmarks Suite             |

| EIB   | Element Interconnect Bus                                |

| FSM   | Finite State Machine                                    |

| FPGA  | Field-Programmable Gate Array                           |

| FPL   | Field Programmable Logic                                |

| GMAP  | Greedy Mapping Algorithm                                |

| GPIO  | General Purpose Input Output                            |

|       |                                                         |

| GPIPS          | General Purpose Image Processing System    |

|----------------|--------------------------------------------|

| GPU            | Graphic Processing Unit                    |

| HBM            | Hard Bus Macro                             |

| IC             | Integrated Circuit                         |

| ICAP           | Internal Configuration Access Port         |

| IT             | Iteration Count                            |

| JCAP           | Virtual Internal Configuration Access Port |

| LB             | Lower Bound                                |

| MDist          | Manhattan Distance                         |

| MIC            | Memory Interface Controller                |

| MMS            | Multimedia System                          |

|                | ·                                          |

| MMS25<br>MMS40 | Multimedia System with 25-Cores            |

|                | Multimedia System with 40-Cores            |

| MPSoC          | Multiprocessors System-on-Chip             |

| MST            | Master Burst                               |

| MT             | Mersenne Twister                           |

| MTT            | Multiple Target Tracking                   |

| MWAG           | Multi-Window Application with Graphics     |

| MWA            | Multi-Window Application                   |

| MWD            | Multi-Window Display                       |

| NCA            | Node Configuration Architecture            |

| NCD            | Native Circuit Description                 |

| NCG            | Node Configuration Graph                   |

| NoCem          | Network on Chip emulator                   |

| NoC            | Network on Chip                            |

| OP             | Optimum Solution                           |

| OPB            | On-Chip Peripheral Bus                     |

| OS             | Original Size                              |

| OSA            | Optimized Simulated Annealing              |

| P2P            | Point to Point                             |

| PB             | Partial Bitstream                          |

|                |                                            |

| PBB     | Partial Branch-and-Bound Algorithm                   |

|---------|------------------------------------------------------|

| PCAP    | Parallel Configuration Access Port                   |

| pdf     | Posterior Density Function                           |

| PE      | Processing Element                                   |

| PFMAP   | Particle Filter Mapping                              |

| PIP     | Picture in Picture                                   |

| PN      | Particle Number                                      |

| PNoC    | Programmable Network on Chip                         |

| PPE     | Power Processor Element                              |

| PR      | Partial Reconfiguration                              |

| PRNG    | Pseudo Random Number Generator                       |

| PRT     | Pulse Repetition Time                                |

| PS      | Partial Sum                                          |

| RA      | Reconfigurable Area                                  |

| RAMPSOC | Runtime adaptive multi-processor system-on-chip      |

| RCT     | Router Configuration Topology                        |

| RL      | Run Length                                           |

| RPE     | Reconfigurable (Image) Processing Element            |

| RRR     | Reconfiguration Repetition Rate                      |

| RSTA    | Router-Switch Topology Architecture                  |

| ReCoSoC | Reconfigurable Communication-centric Systems on Chip |

| ReNoC   | Reconfigurable Network on Chip                       |

| SA      | Simulated Annealing                                  |

| SIR     | Sequential Importance Re-sampling                    |

| SoC     | System On Chip                                       |

| SPE     | Synergestic Processor Element                        |

| SRAM    | Static Random Access Memory                          |

| SS      | Space Savings                                        |

| OSA     | Optimized Simulated Annealing                        |

| TGFF    | Task Graphs for Free                                 |

| TSV     | Through Silicon Via                                  |

|         |                                                      |

| TTG  | Task Traffic Graph                                       |

|------|----------------------------------------------------------|

| VHDL | Very High Speed Integrated Circuits Hardware Description |

|      | Language                                                 |

| VIP  | Virtual Point-to-Point                                   |

| VOPD | Video Object Plane Decoder                               |

| VPU  | Video Processing Unit                                    |

| WC   | Worst Case                                               |

| WF   | Wavefront                                                |

#### 1. MOTIVATION

Today, most of the data intensive applications (e.g image, video, signal processing) are running on embedded multi-core architectures. On a multi-core architecture, there are several small cores which run mostly at lower frequencies. Increasing the number of cores leads to an increase in the number of messages communicated between them. This may end up with a reduced performance and increased energy consumption. Hence, the overall performance of a multi-core system is being affected not only by the computation load but also by the communications infrastructure.

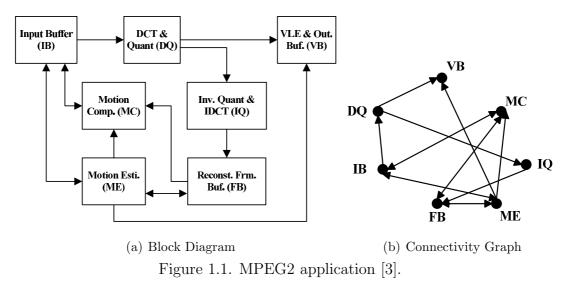

In Figure 1.1 embedded MPEG2 application is given. Here, while rectangular shapes represent the components of this embedded application (see Figure 1.1a), arrows between these components represent the communication interconnects of the application. Similarly, Figure 1.1b shows the connectivity of the components of this application.

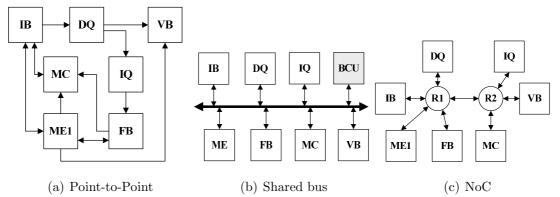

There are, mainly, three on-chip communication architectures to connect the components of this embedded application. Figure 1.2 shows these possible architectures. Figure 1.2a can be the first choice, where each component is directly connected to each other via dedicated wires. Such an approach is called Point-to-Point (P2P). The second choice of on-chip communication architectures can be connection of these components via shared bus (see Figure 1.2b). As an alternative way, components can be connected

Figure 1.2. Possible on-chip communication architectures for MPEG2 application [3].

through routers in a Network-on-Chip (NoC) architecture as given in Figure 1.2c.

Here, the fastest communication architecture is the P2P architecture (see Figure 1.2a) where components are directly connected. Although P2P is the fastest solution among all these three communication architectures (see Figure 1.2), it turns out to be a power- and area-hungry solution as the number of cores increases. In shared bus communication architecture, component pairs communicate through a bus in different time slots (see Figure 1.2b). Here, the scheduling is done through a Bus Control Unit (BCU). Shared bus can be a good candidate if there are not too many connected components or cores. Like P2P, as the number of cores and message requests between these cores increase, shared bus approach becomes not scalable, as well [3].

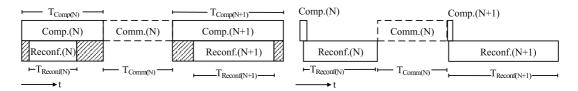

In the last decade, the NoC has been proposed as an alternative to reduce power consumption and has been widely adopted by the SoC community. The third choice of on-chip communication architectures can be NoC architecture, where cores communicate through router elements (see Figure 1.2c). Although NoC architectures propose generic solutions and they are scalable, there are various parameters which affect the performance of NoC communication architecture directly or indirectly. Most important ones are mapping and routing algorithms, network topology, switching method, router architecture and link bandwidth. As the number of cores increase, routers become the bottleneck of NoC architectures because of the congestion and contention delays. In order to reduce negative impacts of routers, the first approach can be reduction the number of routers in a given NoC architecture. Hence, recent NoC studies [12–18] try to suppress the drawbacks of routers used in both packet and circuit switched networks. The best way to relieve traffic density of routers and links can be reduction of contention and congestion delays. The second choice can be applying effective scheduling, mapping and routing processes to the NoC architectures. If the mapping and routing processes are not carried out properly, then improving other parameters will not improve the performance of NoC significantly. As a result of these, we firstly developed efficient mapping and routing algorithms for various NoC architectures in the scope of this thesis (see Chapters 9 and 10). By utilizing these efficient algorithms, we also propose dynamically reconfigurable point-to-point (DRP2P) interconnects for setting up direct connection between two communicating units before the communication starts [19]. In order to increase efficiency of DRP2P, we take the advantage of mapping and routing algorithms, which are mainly developed for NoC architectures: if the communicating nodes are located in an inefficient manner, the reconfiguration area might be larger than as expected. Increase in the reconfigurable area causes an increase in the reconfiguration time as well. Hence, a careful mapping strategy must be applied to the DRP2P for a successful design. In a similar manner, routing of interconnects must be carried out in a wise way such that interconnects do not exceed the boundaries of the pre-selected reconfigurable area. As a result of this, a smart routing must be applied to the DRP2P in order to keep the reconfigurable area as small as possible.